简单搜集整理

在半导体制造领域,技术节点(Technology Node 或 Process Node)是指集成电路(IC)制造工艺的一个阶段性发展指标:

- 早期,技术节点与晶体管的物理尺寸直接相关,比如栅极长度(Gate Length)或M1层间距的半间距(M1 Half-Pitch);

- 现代,技术节点更多是行业中描述工艺先进性的一种标识符,而不再直接对应某个物理尺寸。

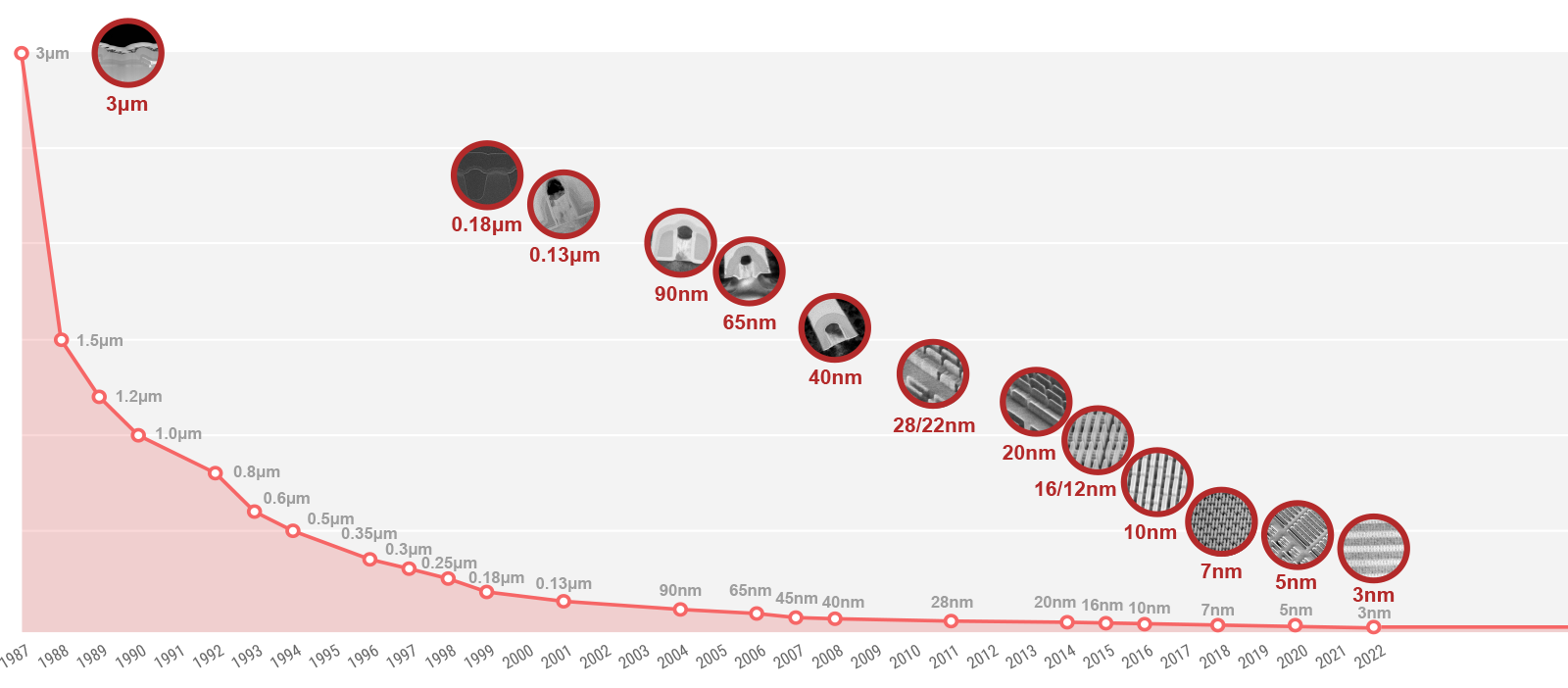

自2017年起,节点名称几乎完全被营销策略所主导。一些顶尖晶圆厂模糊地使用节点名称来代表稍加修改的工艺技术。 此外,各晶圆厂间晶体管的尺寸、密度和性能也不再具有直接的可比性。例如,Intel的10nm节点在性能和密度上与其他厂商的7nm节点相当,而Intel的7nm节点则与其他厂商的5nm节点相当。

图片来源: TSMC

图片来源: TSMC

术语

- Gate Length(栅极长度):控制晶体管开关的区域长度,是技术节点的早期定义基础。

- Transistor Density(晶体管密度):单位面积内集成的晶体管数量,影响芯片性能和效率。

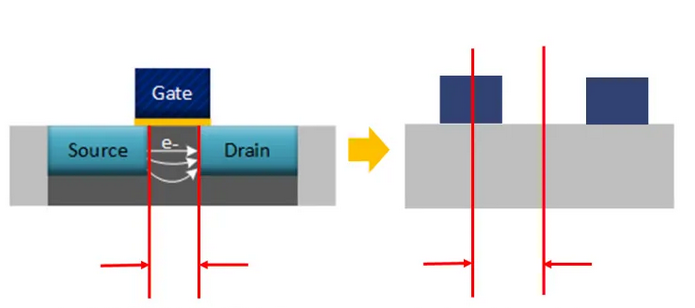

- Fin Field-Effect Transistor(FinFET晶体管架构):一种三维晶体管设计,提高性能并降低功耗。

- Extreme Ultraviolet Lithography(极紫外光刻,EUV),用于制造小于7nm节点的核心光刻技术。

- High-k Dielectrics(高k介质):用于减少漏电流并提升晶体管性能的新型绝缘材料。

命名法

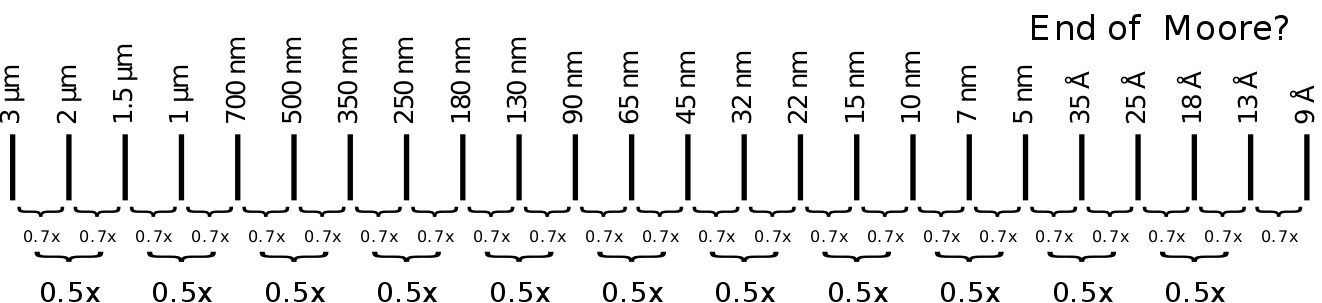

推动工艺节点缩小的核心动力是摩尔定律(Moore's Law)。为了实现晶体管密度的翻倍,每个节点的接触栅极间距(Contacted Poly Pitch, CPP)和最小金属间距(Minimum Metal Pitch, MMP)需要大约按0.7倍的比例缩小。

图片来源:wikichip

发展

早期技术节点:尺寸驱动

技术节点的名称最初直接与晶体管的物理尺寸相关,例如栅极长度或源极/漏极之间的距离(Channel Length)。例如:

- 10µm节点(1970年代):晶体管栅极长度约为10微米。

- 1µm节点(1980年代):栅极长度缩小至1微米。

晶体管尺寸缩小(Scaling)是摩尔定律(Moore's Law)的核心驱动力,即每隔约两年,单位面积内的晶体管数量会翻倍,从而提升计算能力。

从微米到纳米:密度为王

随着尺寸逐渐进入纳米级别(nanometer scale),技术节点不仅表示物理尺寸,还与以下指标挂钩:

- 晶体管密度:每平方毫米的晶体管数量。

- 功耗降低(例如更小的漏电流)。

- 性能提升(更快的开关速度)。

例如:

- 90nm节点(2004年):仍以晶体管物理尺寸为参考。

- 45nm节点(2007年):引入了高k介质(High-k Dielectrics)和金属栅极(Metal Gate)。

- 22nm节点(2011年):Intel首次使用FinFET晶体管架构(Fin Field-Effect Transistor)。

现代节点虚拟化(等效?)

现代技术节点(如14nm、7nm)不再严格对应晶体管的物理尺寸,而是代表制造工艺的整体进步。例如:

- 14nm节点:栅极长度可能为20nm以上,但它指代晶体管密度和性能的一个工艺水平。

- 7nm节点:代表了更高的晶体管密度,但实际尺寸可能远大于7nm。

涉及以下东西:

晶体管架构(Transistor Architecture):

- FinFET(鳍式场效应晶体管):用于22nm及后续工艺。

- GAA(Gate-All-Around):3nm节点引入的下一代晶体管架构。

光刻技术(Lithography Technology):

- 深紫外光刻(DUV):用于28nm到14nm节点。

- 极紫外光刻(EUV):用于7nm及更小节点。

材料创新:

- 使用高k/金属栅极(High-k/Metal Gate)提升性能。

- 新的低介电常数材料(Low-k Dielectrics)降低功耗。

参考

- https://en.wikipedia.org/wiki/Semiconductor_device_fabrication

- https://en.wikichip.org/wiki/technology_node

- https://zhuanlan.zhihu.com/p/680163027

- 关于芯片的7nm到底是个啥