简单梳理一下

前道、后道?? 前段(端)、后段(端)??

这几个术语在中文语境中似乎用的很乱。

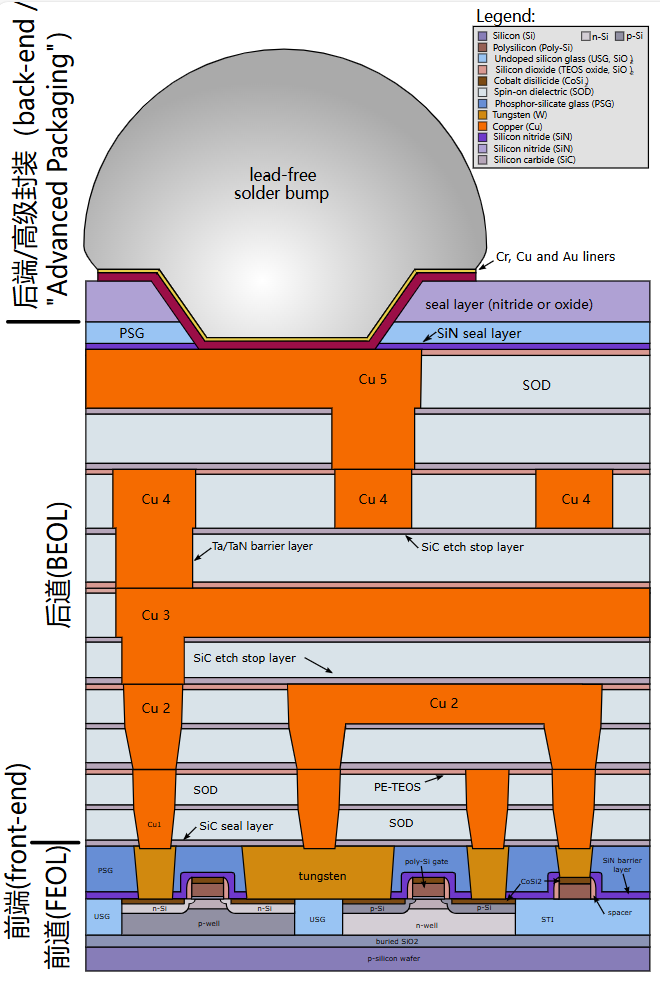

- 【前道工艺】FEOL(Front end of line):集成电路制造的第一阶段,在半导体基底上会被加工出各种单个元件(如晶体管、电容、电阻等)的图案。通常涵盖从工艺开始到金属互连层沉积之前的所有步骤(不包括金属互连层的沉积)13

- 【后道工艺】BEOL(Back end of line):集成电路制造的第二阶段,主要在已经完成器件图案化的晶圆上沉积金属互连层(将单个器件(如晶体管、电容、电阻等)互连起来,形成完整的电路)。23

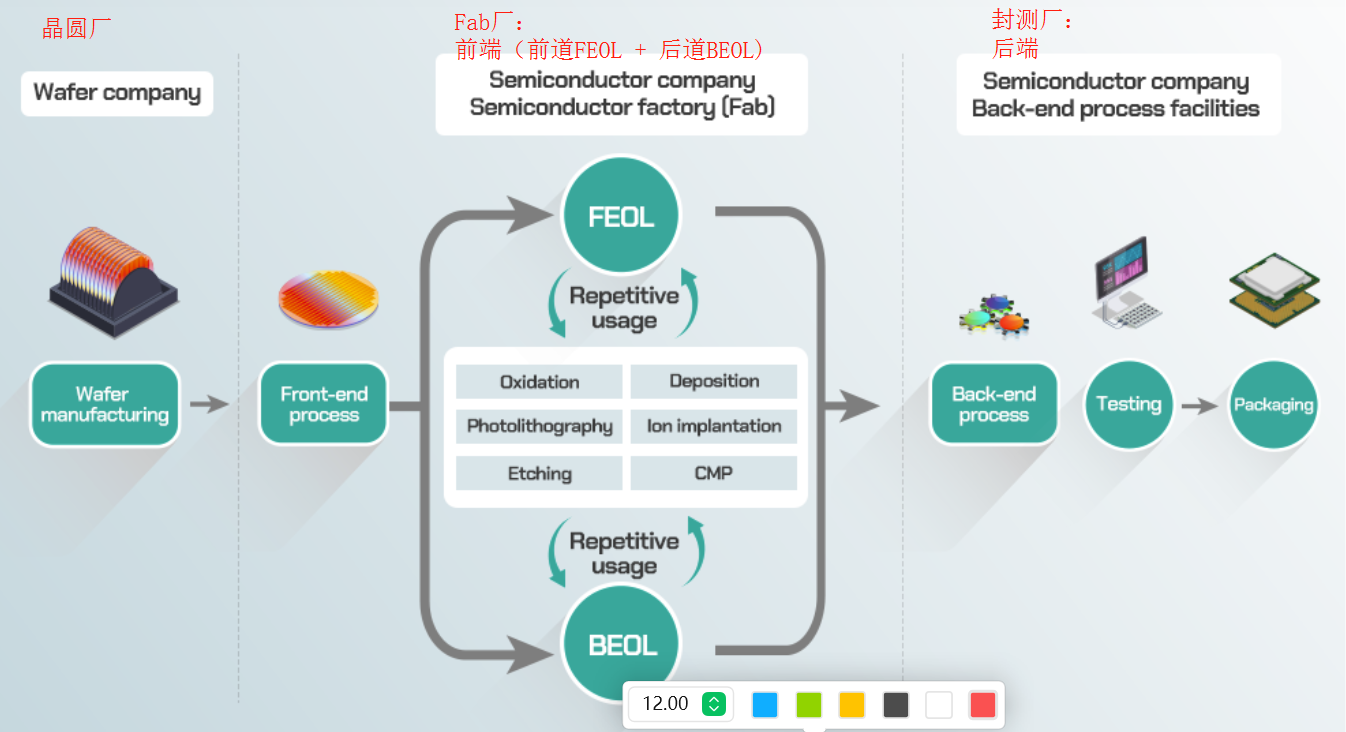

- 【前端工艺】Front end process:包括FEOL和EBOL。在晶圆厂(fab)的洁净室内完成。

- 【后端工艺】Back end process:在EBOL之后,也叫后制造工艺(post-fab),通常不在洁净室内完成,且往往由不同的公司负责。后端工艺包括晶圆测试、晶圆背面研磨、芯片分离、芯片测试、IC封装以及最终测试。2

图片来源: Fundamentals of Layout Design for Electronic Circuits

- 【中道工艺】MEOL(Middle End of Line):随着工艺节点的缩小,制造流程变得更加复杂,将FEOL和BEOL中某些工艺独立出来。主要任务是连接 FEOL 阶段中制造完成的器件(如晶体管)与 BEOL 阶段中的金属互连层,为信号传输和电路连接打下基础。

IDM 与 Fabless、Foundry、OSAT

- IDM(Integrated Device Manufacturer):设计和制造都在公司内部完成。早期的半导体公司(如英特尔、德州仪器)采用该模式

- Fabless:指专注于集成电路设计的公司,不拥有自己的晶圆制造工厂(fab),而是将芯片的制造外包给第三方晶圆代工厂(Foundry)。4

- Foundry:指专门提供芯片制造服务的公司。拥有自己的晶圆制造工厂,并为Fabless公司提供芯片代工服务。5

- OSAT(Outsourced Semiconductor Assembly and Test):外包半导体封装与测试服务商。OSAT 公司专门为半导体设计公司(Fabless)和晶圆代工厂(Foundry)提供芯片的封装(Assembly)和测试(Test)服务。

- 【流片】Tapeout:指代芯片设计完成后,正式将设计数据(通常是 GDSII 或 OASIS 格式文件)交付给晶圆代工厂(Foundry)进行制造的过程。6

由来:在早期,芯片设计完成后,设计文件会被物理记录在磁带(tape)上,然后交付给代工厂。

Die 与 Chip

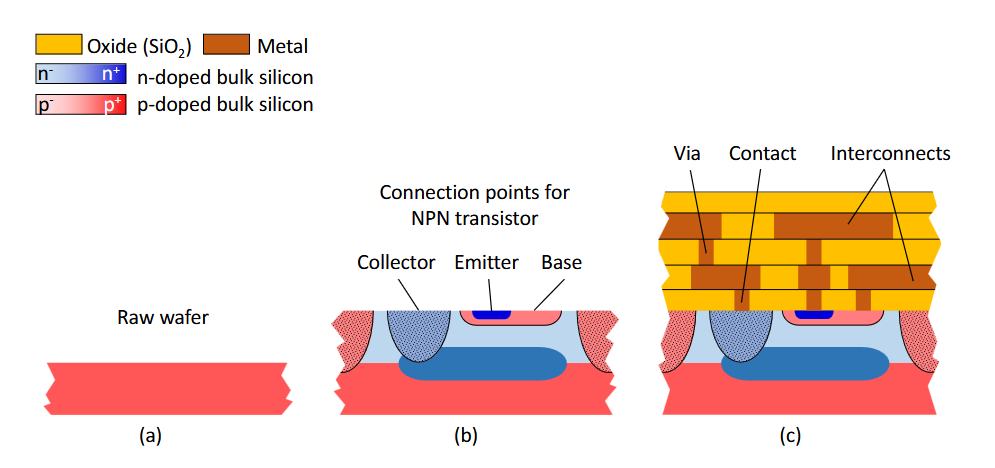

在晶圆(Wafer)上制造完成的电路单元称为 Die。将晶圆切割成单个 Die。对 Die 进行封装和测试,成为成品 Chip。

- Die:是芯片的核心部分,通常由晶体管、电阻、电容等组成,完成了设计所需的全部电路功能。它是晶圆(Wafer)制造完成后,通过切割(Dicing)得到的最小功能单元。

- Chip:对 Die 进行封装(Packaging)和测试(Testing)后的最终产品。它还包括引脚(Pins)或焊球(Balls),用于与外部电路(如 PCB)连接。一个Chip中可以封装多个Die。

Die Bonding 与 Eutectic Bonding

- 【共晶】Eutectic Bonding:一种利用 共晶合金 的熔点特性,将芯片(Die)通过焊料(例如金锡合金)与基板连接的工艺。在这个过程中,共晶材料在特定的温度下熔化并形成牢固的金属结合。

- 【固晶】Die Attach, Die Bonding:将芯片(Die)通过非金属粘接材料(如导电银胶或绝缘环氧树脂)固定到封装基板或支架上的工艺。与共晶不同,固晶主要使用胶体而非金属作为粘接材料。

Eutectic /juːˈtɛktɪk/ 是一个来自希腊语的术语,意为“容易熔化”(希腊语中 eu- 表示“好”或“容易”,tectos 表示“熔化”)。在材料科学和半导体领域,Eutectic 通常翻译为 “共晶”,具体是指一种 多组分合金或混合物,它在某一特定比例下具有最低的熔点,并能以液相直接凝固为固相,而不经历其他中间相的生成。例如,金锡合金(Au-Sn)的共晶点是 280°C。

Ingot

Ingot(硅单晶锭) 是通过半导体工艺生产的高纯度硅单晶棒。通常是直拉法或区熔法。上图来自wikipedia7。

生产方式

- 直拉法(Czochralski, CZ):最常见的硅单晶生长工艺。通过将种子晶体浸入熔融硅中,然后缓慢旋转和拉升,形成单晶硅锭。适用于大尺寸晶圆(如 200mm、300mm)。7

- 区熔法(Float Zone, FZ):通过电磁感应将硅棒局部加热至熔化,逐段移动熔区以提纯并生长单晶。纯度更高。

直拉法由波兰科学家 Jan Czochralski 于 1916 年发明。在波兰语中,Czochralski 的标准发音为 /tʂɔˈxral.ski/,类似于“楚克拉尔斯基”或“乔克拉尔斯基”。

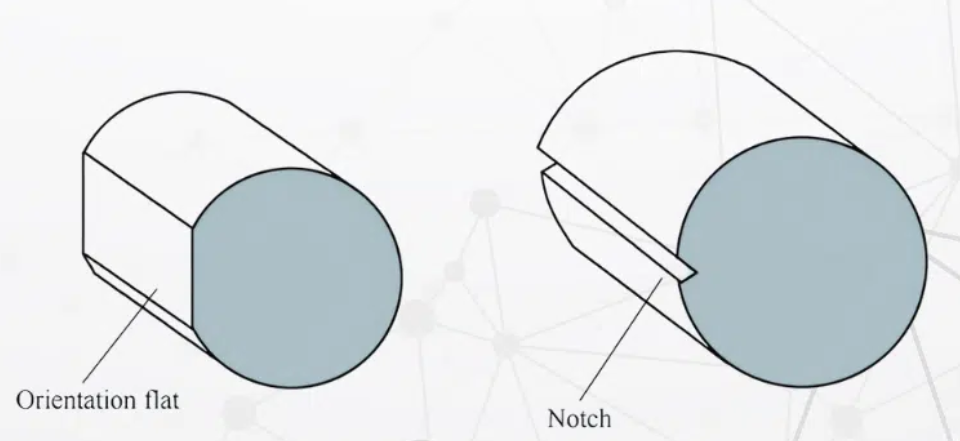

Flat 与 Notch

Flat 和 Notch 是半导体制造中用于标识和定位晶圆(Wafer)方向和晶体取向的特定结构。早期晶圆(6寸及以下)用Flat,但随着晶圆尺寸的增大和自动化设备的普及,Notch 已成为主流标识方式。

- Flat(平边):是指在晶圆边缘切去的一段平直的部分。位于晶圆的边缘,占据一段相对较长的直线。

- Notch(凹槽):是指在晶圆边缘刻出的一个小的 V 型缺口或凹槽。位于晶圆的边缘,占据很小的区域。

换个角度

半导体 FAB 工艺包括从 晶圆制造 到 晶圆加工(FEOL/MEOL/BEOL) 再到 封装与测试 的完整流程。关键环节包括 光刻(Photolithography)、刻蚀(Etching)、薄膜沉积(Deposition) 和 金属互连(Interconnects),这些工艺共同支持芯片的高性能和高集成度。

图片来源:Semiconductor Front-End Process Episode 2

晶圆制造(Wafer Manufacturing)

将高纯度 多晶硅(Polysilicon) 制备成 单晶硅锭(Ingot),然后切割成 晶圆(Wafer)。

- Czochralski Method (CZ):直拉法,用于生长单晶硅。

- Wafer Polishing:晶圆抛光,确保表面平整。

前道工艺(Front-End of Line, FEOL)

在晶圆上制造晶体管(Transistor)等基本器件。

- 氧化(Oxidation):在晶圆表面生长一层氧化硅(SiO₂)作为绝缘层。

- 光刻(Photolithography):使用光刻胶(Photoresist)和掩膜版(Mask)将电路图案转移到晶圆上。

- 刻蚀(Etching):去除不需要的材料,形成所需的图案。包括

- Dry Etching:干法刻蚀(等离子刻蚀)。

- Wet Etching:湿法刻蚀(化学溶液刻蚀)。

- 离子注入(Ion Implantation):注入掺杂剂(如硼或磷)调节硅的电学特性。掺杂(Doping)。

- 薄膜沉积(Thin Film Deposition):在晶圆表面沉积导电或绝缘薄膜。

- CVD (Chemical Vapor Deposition):化学气相沉积。

- PVD (Physical Vapor Deposition):物理气相沉积。

- Epitaxial Growth:外延生长。

- 退火(Annealing):通过加热修复晶体结构,激活掺杂剂。

中道工艺(Middle-End of Line, MEOL)

连接晶体管的源极、漏极和栅极,形成基本电路单元。

术语:

- Contact Formation:接触孔制作。

- Local Interconnects:局部互连。

后道工艺(Back-End of Line, BEOL)

构建多层金属互连网络,将器件连接成完整电路。

- 金属沉积(Metal Deposition):在晶圆上沉积金属层(如铜或铝)作为导电路径。铜互连(Copper Interconnects)。

- 化学机械平坦化(CMP):Chemical Mechanical Polishing,平整金属层和介电层,确保多层结构均匀。

- 通孔制作(Via Formation):在金属层之间刻蚀通孔并填充金属实现垂直连接。

晶圆测试(Wafer Testing)

在晶圆阶段对每个芯片(Die)进行电学测试。

术语:

- Probe Test:探针测试。

- Yield:良品率。

封装与测试(Packaging & Final Testing)

将切割后的芯片(Die)封装为可用的成品。

术语:

- Dicing:晶圆切割。

- Wire Bonding:焊线。

- Micro-Bump:微凸点。

- Flip-Chip:倒装芯片。

- Final Test:最终测试。

其他

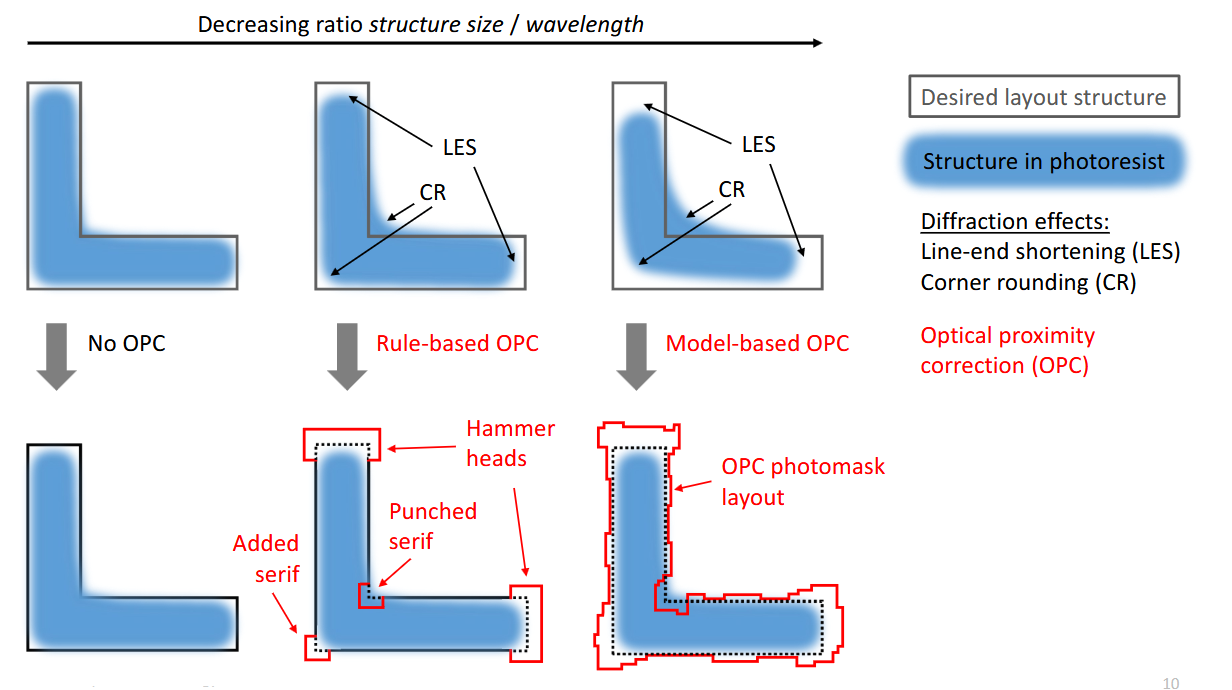

OPC

光学临近效应(Optical Proximity Correction,OPC)是一种基于模型的数学技术,用于修正光刻过程中由于光学效应(如衍射、干涉)和工艺效应(如刻蚀、抗蚀剂行为)导致的图形失真。

图片来源: Fundamentals of Layout Design for Electronic Circuits

OPC 有两种类型:

Rule-Based OPC(基于规则的 OPC)

基于一组预定义规则(如线宽调整、边缘偏移)进行简单的修正。快速且计算需求低。适用于早期工艺节点或简单图案。但是对复杂图形的修正能力有限,精度较低。

Model-Based OPC(基于模型的 OPC)

使用光学仿真工具,基于光学模型和刻蚀模型对掩膜版图案进行优化。精度高,可处理复杂图形,是现代先进工艺(如 7nm、5nm)中主流的 OPC 方法。但是计算复杂度高,耗时较长。

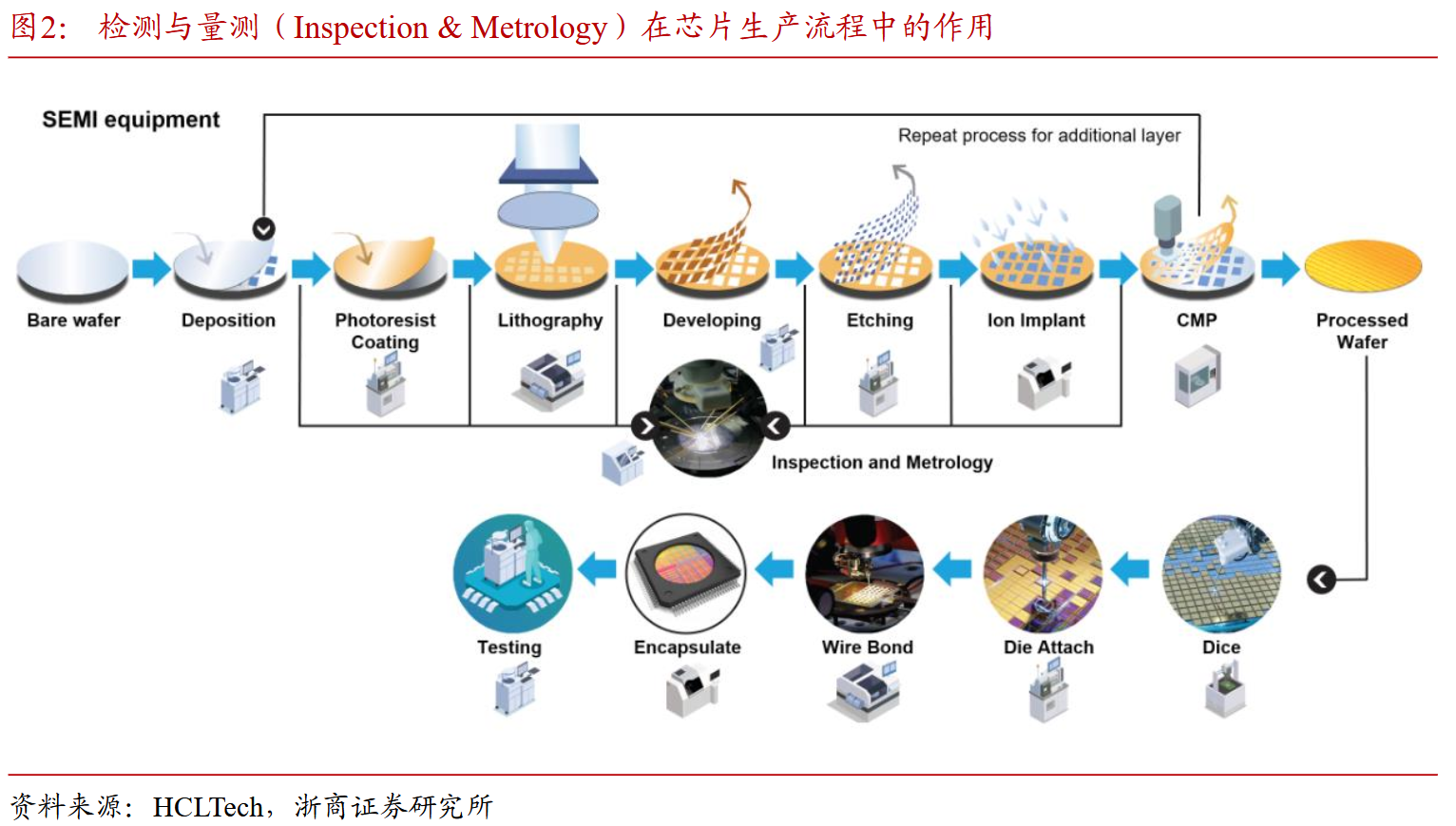

Metrology 与 Inspection

- Metrology: 指量测(Measurement)的科学和技术,用于测量半导体制造过程中关键参数(如尺寸、厚度、形貌等)。

- Inspection: 指检测(Inspection)设备,用于发现和识别晶圆或掩膜版上的缺陷(Defects)。

量检测设备在FAB中的应用(加黑的属于SEM):

| 产品 | 薄膜沉积 | 光刻 | 掩膜 | 刻蚀 | 离子注入 | CMP | 清洗 |

|---|---|---|---|---|---|---|---|

| 掩膜版缺陷检测设备 | - | - | ☆ | - | - | - | - |

| 无图形晶圆缺陷检测设备 | ☆ | ☆ | - | ☆ | ☆ | ☆ | ☆ |

| 图形晶圆缺陷检测设备 | - | ☆ | - | ☆ | ☆ | ☆ | ☆ |

| EBI | - | ★ | - | ★ | ★ | ★ | - |

| DR-SEM | - | ★ | - | ★ | ★ | ★ | - |

| - | - | - | - | - | - | - | - |

| 关键尺寸量测设备 | - | - | - | ☆ | - | - | - |

| CD-SEM | - | ★ | - | ★ | - | - | - |

| 套刻精度量测设备 | - | ☆ | - | - | - | - | - |

| 晶圆介质薄膜量测设备 | ☆ | ☆ | - | - | - | - | - |

| X光量测设备 | ☆ | - | - | - | ☆ | - | ☆ |

| 掩膜版关键尺寸量测设备 | - | - | ☆ | - | - | - | - |

| 三维形貌量测设备 | - | - | - | - | - | ☆ | ☆ |

| 晶圆金属薄膜量测设备 | ☆ | - | - | - | - | ☆ | - |

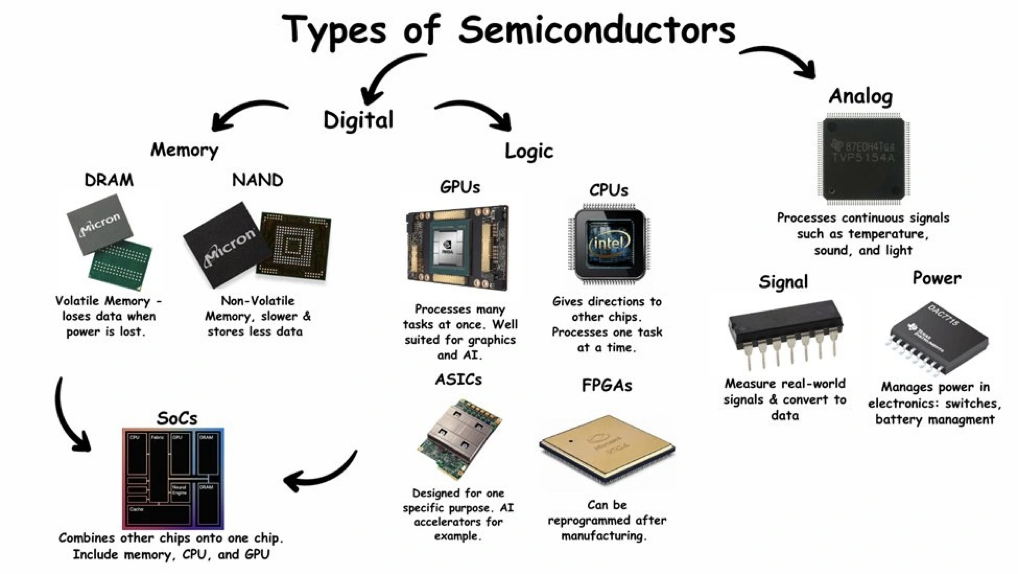

Logic, Memory 与 Analog 芯片

- 逻辑芯片(Logic Chips):处理数字信号,执行布尔逻辑(Boolean Logic)运算,如CPU、GPU等。

- 存储芯片(Memory Chips):存储和检索数据,包括DRAM(动态内存)和NAND(闪存)。

- 模拟芯片(Analog Chips):处理连续信号,如电压和电流,应用于音频设备和传感器。

- 数字-模拟混合芯片(Mixed-Signal Chips):实现数字信号和模拟信号间的转换,如ADC和DAC。

- 专用集成电路(ASIC):为特定用途设计的高效定制芯片,如加密挖矿芯片。

- 现场可编程门阵列(FPGA):可重配置芯片,适用于测试和灵活应用开发。

图片来源: https://techovedas.com/13-semiconductor-terms-everyone-must-know/