接前面Quartus Prime Lite小记三,搞定git和Quartus整合后,了解一下Quartus下面的Questa Intel FPGA 这个仿真软件怎么用。

Questa Intel FPGA是什么东西?

ModelSim,Questa,都没有用过;VHDL、Verilog还没开始接触;碰到这一堆堆东西,想简单学学,还真有点不知道怎么入手。

Quartus Prime从21版本开始,带了仿真软件 Questa Intel FPGA(在此之前带的是ModelSim Intel FPGA)。

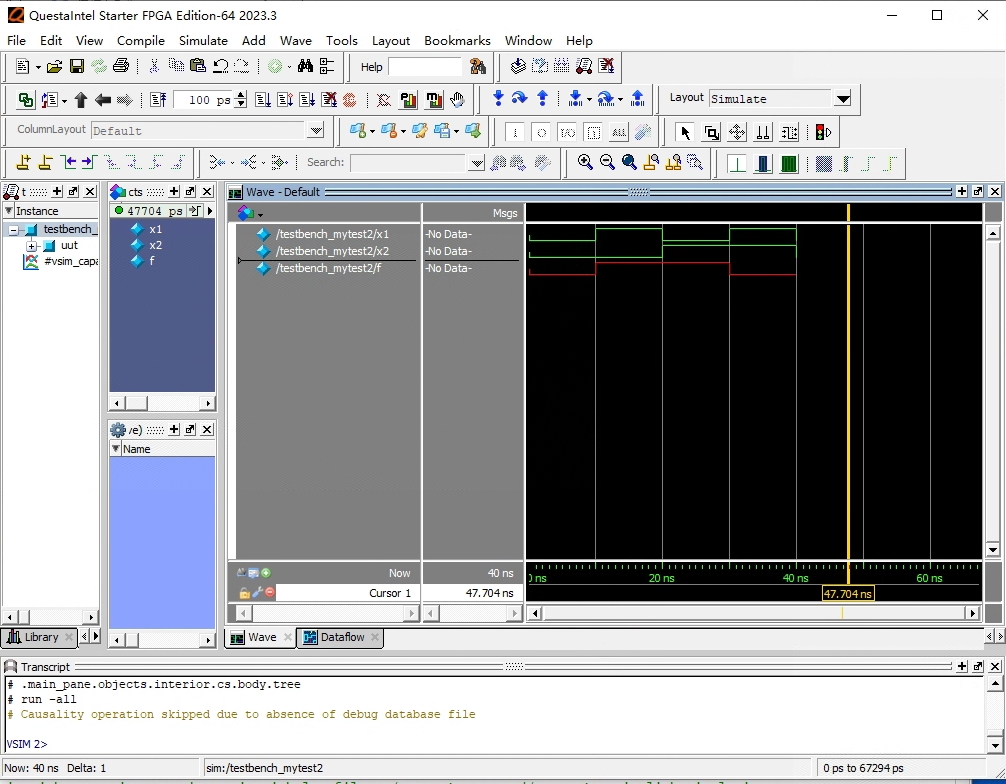

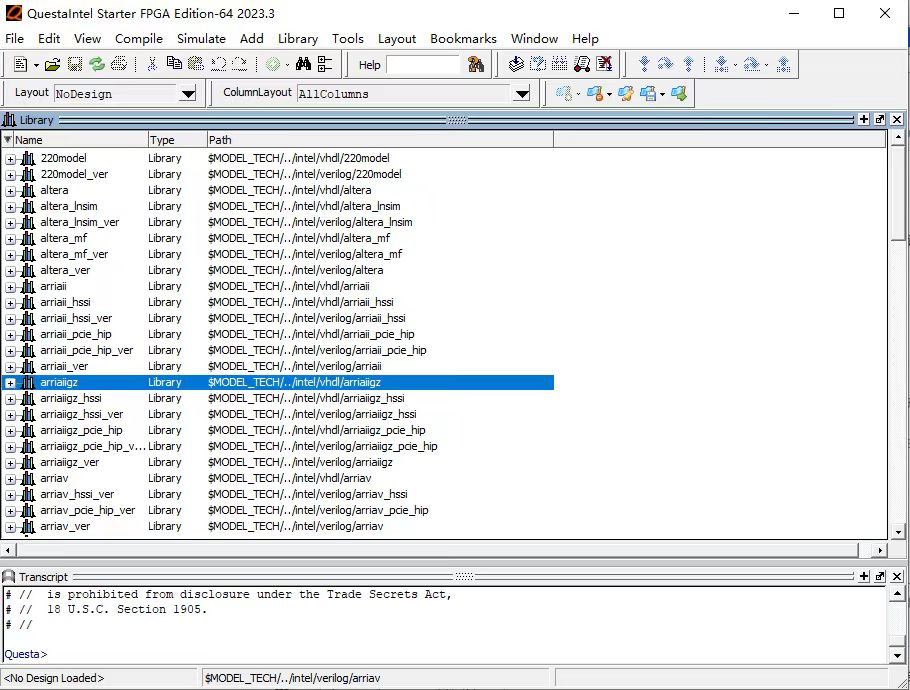

运行界面如下:

Quartus 与 Questa

和Quartus的 Lite版本一样,Questa Intel也提供一个免费版本:

- Intel® Quartus® Prime Lite Edition

- Questa*-Intel® FPGA Starter Edition

Quartus Lite无需License文件,Questa Starter需要在Intel官方免费申领License。

ModelSim 与 Questa

ModelSim 和 Questa 都是是硬件描述语言(HDL)仿真软件,目前都属于西门子。ModelSim最初是由 Model Technology开发,后来被 Mentor Graphics 收购,而 Mentor Graphics 又被 Siemens 收购。

- ModelSim 是一种更基础的仿真工具,适用于教育、小型到中型项目以及个人使用。

- Questa 是一个高级仿真和验证平台,专为大型项目和复杂的系统级验证设计。

ModelSim-Intel 与 Questa-Intel

这两个都是针对Intel FPGA设计优化的仿真软件。在Altera被Intel收购前,他们分别叫ModelSim-Altera与Questa-Altera。

Quartus Prime 从版本 21开始,包含Questa-Intel仿真器。在21版本之前,它包含ModelSim仿真器。

Quartus lites版本安装后,starter版本的questasim.exe位于D:\intelFPGA_lite\23.1std\questa_fse\win64。

ModelSim-Intel 与 Questa-Intel 的 Starter版本都是免费使用的,在Intel官方可以下载。(安装包和标准版是同一个,安装时有选项可以选择Starter)

ModelSim-Intel 只能下载到 20.1,可能也不会有21了。

Questa的starter版本的License问题

尽管是免费申领,但是这个操作挺繁琐...

申请License文件

访问官方,注册账户

选中如下项,点击继续Questa*-Intel® FPGA Starter Edition (License: SW-QUESTA)

添加计算机

- 输入网卡地址NIC-ID(12个16进制数,不适用:或-分隔符。

申请成功就会发送我们的email中。

添加 license 文件

在 Quartus 的 Tools菜单中,点击License Setup...调出设置页面。把license文件路径设置为环境变量LM_LICENSE_FILE

启动 QuestaSim

此时就可以启动questasim了,不过,要注意,由于是starter版本,只能启动一个实例!!!

可执行程序路径:

D:\intelFPGA_lite\23.1std\questa_fse\win64\questasim.exe

配置 Quartus

在Quartus中创建新项目时,可以配置Simulation为Questa Intel FPGA。

相关配置有几处

Tools-> Options...->EDA Tool Options,设置Questa Intel FPGA 的路径 ,大致d:/intelfpga_lite/23.1std/questa_fse/win64Assignments->EDA Tools Settings->Simulation选择Questa Intel FPDATools -> Run simulation Tool -> ...执行

结果:

- .qsf 文件中出现

EDA_SIMULATION_TOOL相关的assignment - 编译时生成 Questa 所需的文件,在

simulation/questa目录下面

quartus_eda

命令行工具quartus_eda用于生成仿真所需的文件(接之前的例子,项目名 mytest3.qpf,源文件mytest2.v),执行:

quartus_eda --read_settings_files=off --write_settings_files=off mytest3 -c mytest3

在文件夹simulation/questa下生成:

- mytest3.sft

- mytest3.vo

当然,再此之前,必须先执行综合(如果没执行的话):

quartus_map --read_settings_files=on --write_settings_files=off mytest3 -c mytest3

注意: eda使用的选型

--read_settings_files=off,并不是说这个命令和.qsf文件无关,而是因为map已经将.qsf的内容消化并写入到了db文件夹下面。eda会直接使用db文件夹中的内容。

使用quartus和questa进行仿真

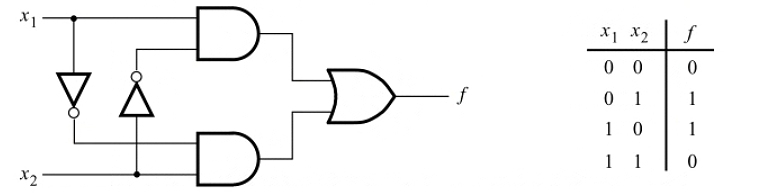

使用前面的简单的组合逻辑电路,试着在quartus界面下跑通questa仿真流程

准备项目

创建一个quartus项目,并添加verilog文件。

- mytest4.qpf

- mytest4.qsf

- mytest2.v (继续使用之前的代码)

mytest2.v的内容如下

module mytest2 (input wire x1, input wire x2, output wire f);

assign f = (x1 & ~x2)|(~x1 & x2);

endmodule

mytest4.qsf内容如下:

set_global_assignment -name FAMILY "MAX 10"

set_global_assignment -name DEVICE 10M50SAE144C8G

set_global_assignment -name TOP_LEVEL_ENTITY mytest2

set_global_assignment -name VERILOG_FILE mytest2.v

set_global_assignment -name ORIGINAL_QUARTUS_VERSION 23.1STD.0

set_global_assignment -name LAST_QUARTUS_VERSION "23.1std.0 Lite Edition"

set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0

set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85

set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 256

set_global_assignment -name EDA_SIMULATION_TOOL "Questa Intel FPGA (Verilog)"

set_global_assignment -name EDA_TIME_SCALE "1 ps" -section_id eda_simulation

set_global_assignment -name EDA_OUTPUT_DATA_FORMAT "VERILOG HDL" -section_id eda_simulation

set_global_assignment -name EDA_GENERATE_FUNCTIONAL_NETLIST OFF -section_id eda_board_design_timing

set_global_assignment -name EDA_GENERATE_FUNCTIONAL_NETLIST OFF -section_id eda_board_design_symbol

set_global_assignment -name EDA_GENERATE_FUNCTIONAL_NETLIST OFF -section_id eda_board_design_signal_integrity

set_global_assignment -name EDA_GENERATE_FUNCTIONAL_NETLIST OFF -section_id eda_board_design_boundary_scan

有意义的主要是前4行。

这时候可以编译项目了。

添加 testbench 文件

要仿真上面的模块,需要先创建一个testbench文件,比如testbench_mytest2.v:

`timescale 1ns / 1ps

module testbench_mytest2;

// Inputs

reg x1;

reg x2;

// Outputs

wire f;

// 实例化要测试的模块

mytest2 uut (

.x1(x1),

.x2(x2),

.f(f)

);

initial begin

// 初始化输入

x1 = 0;

x2 = 0;

// 激励序列

#10 x1 = 1; x2 = 0;

#10 x1 = 0; x2 = 1;

#10 x1 = 1; x2 = 1;

#10 x1 = 0; x2 = 0;

end

endmodule

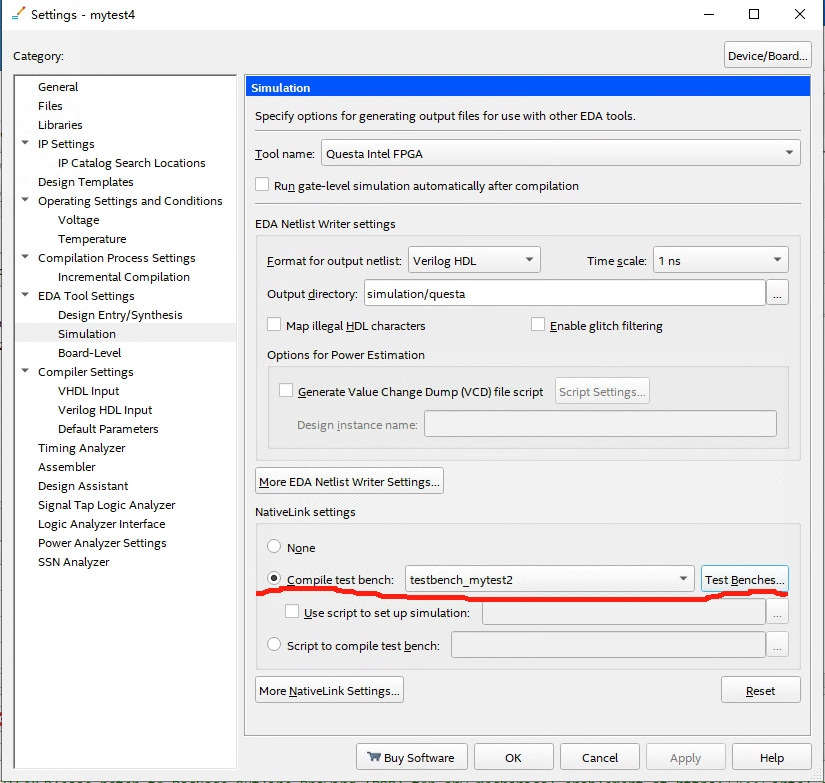

而后进行配置,Assignments->Settings...->EDA Tool Settings->Simulation->NativeLink setting-> Compile test bench

在该页面中,添加我们创建的 testbench_mytest2.v文件。

一通操作过后,我们的.qsf文件长这样:

set_global_assignment -name FAMILY "MAX 10"

set_global_assignment -name DEVICE 10M50SAE144C8G

set_global_assignment -name TOP_LEVEL_ENTITY mytest3

set_global_assignment -name ORIGINAL_QUARTUS_VERSION 23.1STD.0

set_global_assignment -name LAST_QUARTUS_VERSION "23.1std.0 Lite Edition"

set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0

set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85

set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 256

set_global_assignment -name VERILOG_FILE testbench_mytest2.v

set_global_assignment -name VERILOG_FILE mytest2.v

set_location_assignment PIN_6 -to x2

set_location_assignment PIN_7 -to x1

set_location_assignment PIN_8 -to f

set_global_assignment -name EDA_SIMULATION_TOOL "Questa Intel FPGA (Verilog)"

set_global_assignment -name EDA_TIME_SCALE "1 ns" -section_id eda_simulation

set_global_assignment -name EDA_OUTPUT_DATA_FORMAT "VERILOG HDL" -section_id eda_simulation

set_global_assignment -name EDA_GENERATE_FUNCTIONAL_NETLIST OFF -section_id eda_board_design_timing

set_global_assignment -name EDA_GENERATE_FUNCTIONAL_NETLIST OFF -section_id eda_board_design_symbol

set_global_assignment -name EDA_GENERATE_FUNCTIONAL_NETLIST OFF -section_id eda_board_design_signal_integrity

set_global_assignment -name EDA_GENERATE_FUNCTIONAL_NETLIST OFF -section_id eda_board_design_boundary_scan

set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Top

set_global_assignment -name PARTITION_FITTER_PRESERVATION_LEVEL PLACEMENT_AND_ROUTING -section_id Top

set_global_assignment -name PARTITION_COLOR 16764057 -section_id Top

set_global_assignment -name POWER_PRESET_COOLING_SOLUTION "23 MM HEAT SINK WITH 200 LFPM AIRFLOW"

set_global_assignment -name POWER_BOARD_THERMAL_MODEL "NONE (CONSERVATIVE)"

set_global_assignment -name FLOW_ENABLE_POWER_ANALYZER ON

set_global_assignment -name POWER_DEFAULT_INPUT_IO_TOGGLE_RATE "12.5 %"

set_global_assignment -name EDA_TEST_BENCH_ENABLE_STATUS TEST_BENCH_MODE -section_id eda_simulation

set_global_assignment -name EDA_NATIVELINK_SIMULATION_TEST_BENCH testbench_mytest2 -section_id eda_simulation

set_global_assignment -name EDA_TEST_BENCH_NAME testbench_mytest2 -section_id eda_simulation

set_global_assignment -name EDA_DESIGN_INSTANCE_NAME NA -section_id testbench_mytest2

set_global_assignment -name EDA_TEST_BENCH_MODULE_NAME testbench_mytest2 -section_id testbench_mytest2

set_global_assignment -name EDA_TEST_BENCH_FILE testbench_mytest2.v -section_id testbench_mytest2

set_instance_assignment -name PARTITION_HIERARCHY root_partition -to | -section_id Top

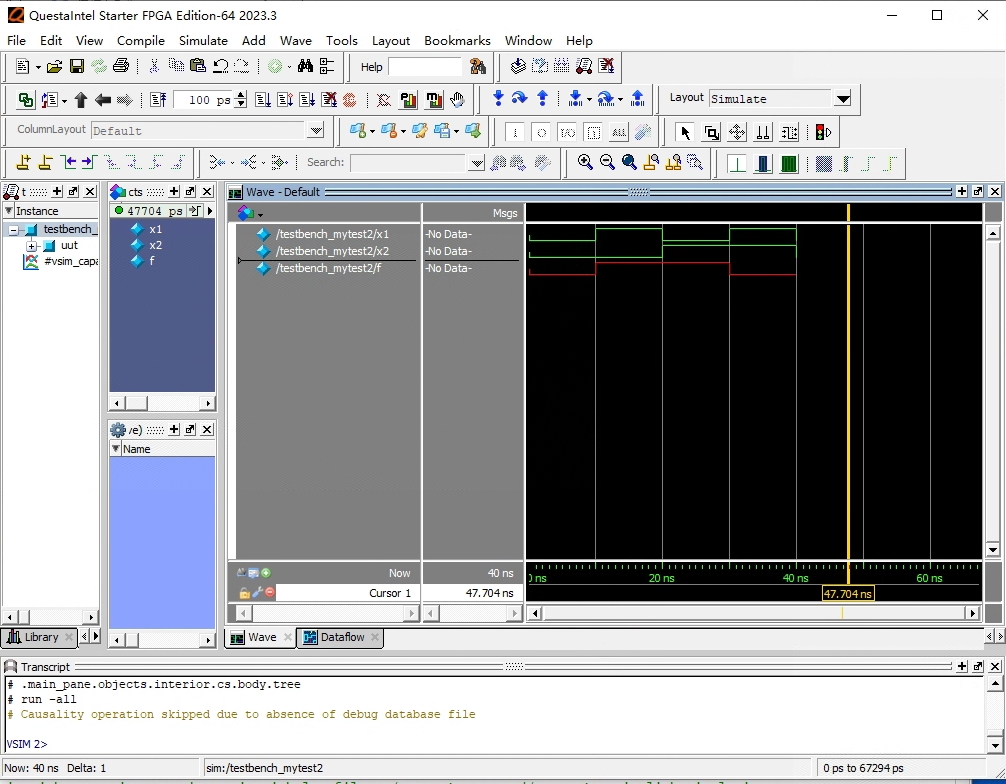

运行仿真

Tools->Run simulation Tool->RTL Simulation

也可以和真值表对一下:

至此,简单的流程算是跑通了,但是背后调用的命令,暂时还是一头雾水。