接前面Quartus Prime Lite小记一,继续野路子补充Quartus基本知识。注:本文内容依然使用 Quartus Prime Lite 23.1进行验证。

Quartus的界面很多人在用,但是用它的界面入门的话,总觉得还缺点东西...,可能命令行更适合我。

工作流程

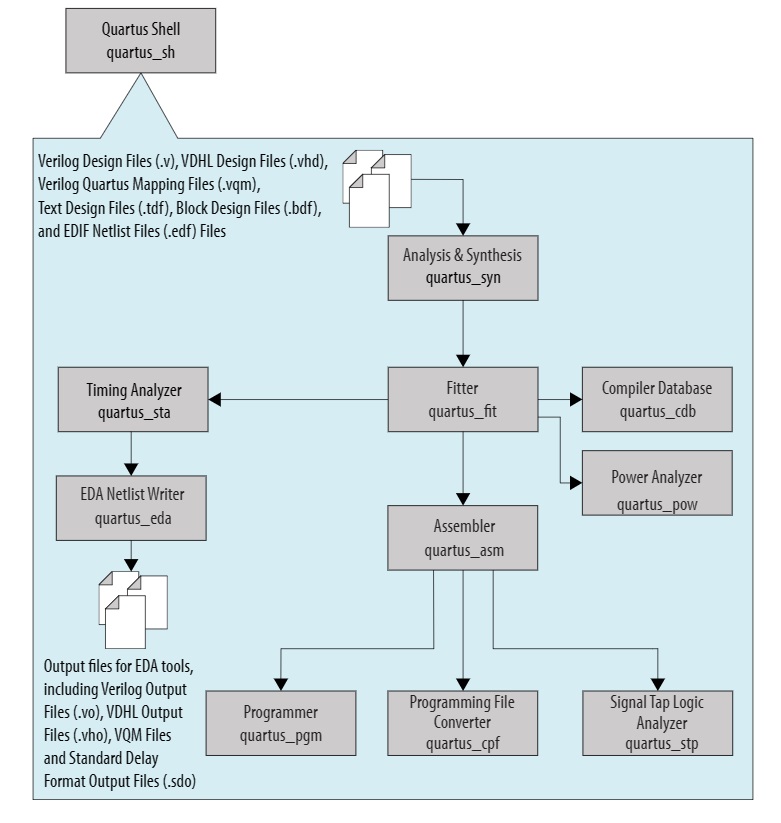

Quartus可以在命令行下工作,典型的工作流如下:

详见:https://www.intel.com/content/www/us/en/docs/programmable/683432/21-4/compilation-with-quartus-sh-flow.html

注意:图中,用于综合的工具叫做

quartus_syn,这个是在Quartus专业版中才有,在我们的Lite版本中,只能使用quartus_map工具!!

暂时只关心几个工具:

| 工具名称 | 功能 | 主要任务 |

|---|---|---|

quartus_map |

综合设计,将高级描述转换为逻辑元素 | - 分析和优化设计代码。 - 进行逻辑综合,映射到 FPGA 的逻辑资源。 - 输出逻辑网表。 |

quartus_fit |

执行布局与布线,将综合的逻辑元素放置到 FPGA 的物理资源上 | - 进行布局,确定元件位置。 - 执行布线,规划连接路径。 - 进行时序分析和优化。 |

quartus_sta |

静态时序分析 | 用于验证数字电路在没有进行实际操作或在没有输入任何实际数据的情况下满足时序要求。 |

quartus_asm |

生成最终的 FPGA 设备配置文件 | - 合并布局与布线结果和引脚分配。 - 输出 .sof 文件和 .rbf 文件。- 确保文件准确反映设计的所有方面。 |

quartus_eda |

EDA网表写入 | 用于与其他电子设计自动化(EDA)工具集成。这包括生成用于仿真和验证的文件,以及为电路板级设计生成其他必需的设计文件。 |

quartus_pgm |

FPGA 设备编程 | - 通过 JTAG 或其他接口将配置文件(如 .sof 文件)下载到 FPGA 或 CPLD 设备。- 支持设备的在线或离线编程。 |

quartus_cpf |

配置文件格式转换 | - 从 .sof 格式转换为 .rbf 或其他格式。- 支持配置文件的压缩和加密等高级特性。 |

查看帮助

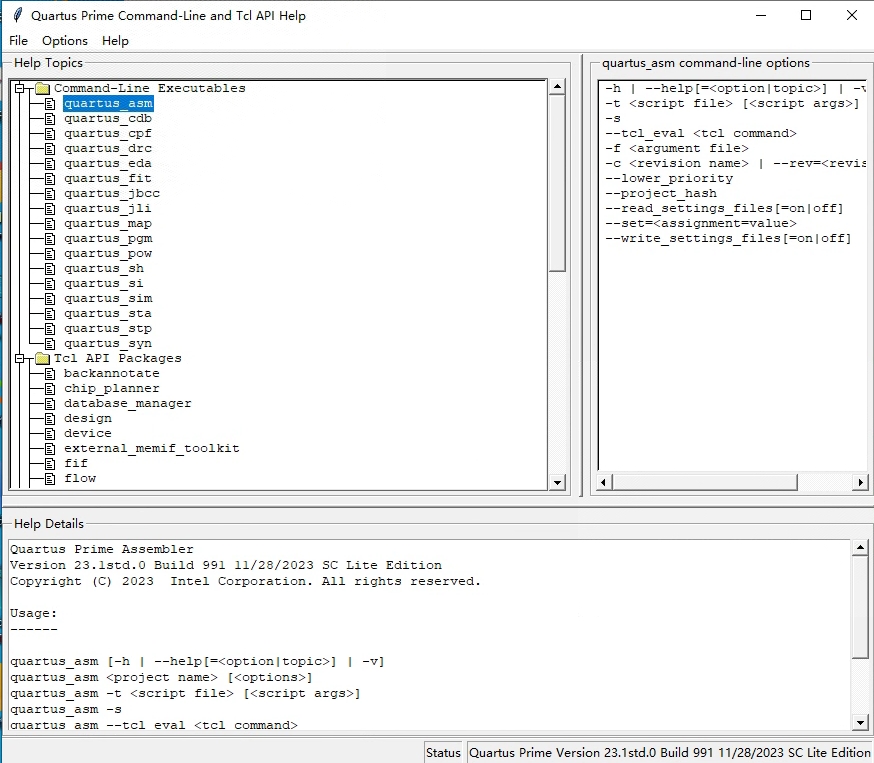

如下命令可以调出帮助页面:

1 | |

参数

手册中说,调用命令时,尽可能使用

--read_settings_files=off和--write_settings_files=off,来优化Quartus读取和更新.qsf文件的方式。

命令行程序执行时,会按照如下顺序读取Assignments

- 命令行参数

- .qsf文件内容

- 工程的数据库(db目录)

- Intel Quartus软件默认值

通过如下命令控制是否去读.qsf文件:

--read_settings_files = on(default)--read_settings_files = off

程序执行结束时,参数写入

- .qsf文件

- 工程数据库(db)

如下命令可以控制是否写入.qsf文件:

--write_settings_files = on(default)--write_settings_files = off

例子

不使用界面,看看只用命令行,如何创建一个项目,并完成编译

创建工程

1 | |

会创建出如下两个文件:

- mytest2.qpf

- mytest2.qsf

qpf文件没什么内容,主要看看.qsf文件:

1 2 3 4 5 6 | |

网上有这个--prepare似乎很少,没找到如何通过命令行指定FAMILY和DEVICE,只能手动修改这个文件了(根据自己的FPGA手动修改)

1 2 | |

源文件

编写一个verilog文件,比如mytest2.v

1 2 3 | |

注意:模块名字和需要和qsf文件中的

TOP_LEVEL_ENTITY匹配。

将该文件加入到.qsf文件内,即加一行

1 | |

如果要绑定引脚,也是需要修改.qsf文件。

编译

源码和项目文件都有了,可以直接编译了...

1 2 3 | |

三条命令执行完,即可在当前目录下得到如下文件:

- mytest2.sof

- mytest2.pof

不想直接敲这么多命令的话,其实下面一条命令也是可以的

1 | |

该命令除了执行我们前面的命令外,还执行

quartus_sta。

清理

要删除各种临时文件,只需要如下命令:

1 | |

注意,这个清理工作是智能的,它只清理mytest2对应的各种产出结果。如果同一个文件夹下还有一个mytest3,mytest3的源码以及各种产出结果,并不会被清理。

TCL脚本

真的像我们这样用命令行的似乎很少。资料找起来有点头大,可能姿势不对...,官方对TCL支持似乎更好。

创建项目

先写一个tcl脚本,比如my_setup.tcl

1 2 3 4 5 6 7 8 9 10 11 | |

而后直接执行它

1 | |

这样就会生成如下文件

- mytest3.qpf

- mytest3.qsf

编译

把我们上个例子中的mytest.v源码拷进来,工程就是全的。直接执行

1 | |

即可完成编译,并生成待烧写文件:

- mytest3.sof

- mytest3.pof

常用文件后缀

前面走马观花看了verilog在Quartus开发最简流程,接触了一些后缀文件。需要再看看

项目文件

前面见到了

- .qpf 项目入口文件

- .qsf 项目配置文件:包括项目使用的 FPGA 设备类型、引脚配置、项目选项、编译设置、时序约束和其他用户定义的设置

手册中还提到(尽管在Prime Lite下没找到如何生成它们)

- .qws 工作区文件(和项目构建无关,纯粹和Quartus界面有关?)

- .qdf 默认配置文件(格式和.qsf一样)

配置文件(烧写文件)

前面编译的结果是 .sof文件,这个文件通常调试,正式发布的话,一般需要转成.pof文件或.jic文件

- .sof 文件(SRAM Object File):这是一个二进制文件,包含 FPGA 的配置数据,通常在开发阶段用于直接通过 JTAG 或其他接口将配置下载到 FPGA 的 SRAM。

- .pof 文件(Programmer Object File):这是一个用于永久编程 FPGA 或 CPLD 的二进制文件,适用于需要将配置数据永久存储在设备中的情况。

- .jic文件(JTAG Indirect Configuration File):这个文件用于定义通过 JTAG 间接配置 FPGA 时所需的数据和参数。

通过 Quartus Prime菜单File->Convert Programming Files... 可以调出这个转换页面。

另外还有

- .rbf 文件(Raw Binary File):

- .hex 文件():一种文本文件...

设计输入

这个表格有点长

| 文件扩展名 | 描述 |

|---|---|

.tdf |

Intel自己的硬件描述语言(Altera HDL),用于硬件描述 |

.vhd, .vhdl |

VHDL源代码文件,用于硬件描述 |

.v, .vlg, .verilog |

Verilog源代码文件,用于硬件描述 |

.sv |

SystemVerilog源代码文件,用于更复杂的硬件描述和验证 |

.vqm |

包含了用于 Quartus 综合器的优化后的 Verilog HDL 代码 |

.edf, .edif, .edn |

电子设计互操作格式文件,用于在不同的CAD工具之间传输设计数据 |

.cpp, .h |

C++源代码和头文件,可能用于FPGA设计中的软件部分或与FPGA交互的外部程序 |

.mdl |

MATLAB Simulink模型文件,用于基于模型的设计和仿真 |

.gdf, .bdf |

图形设计文件,用于Quartus Prime的图形用户界面 |

.qip |

Quartus IP 文件 |

.qdb |

Quartus Database,存储编译后的设计数据 |

.cmp |

Compiler Mapping File,可能用于定义编译器的映射设置 |

.qxp |

Quartus Export Package,用于导出和导入设计的一部分 |

.smf |

Simulation Model File,用于仿真模型 |

.qsys, .ip |

用于定义和实例化系统级设计和IP核 |

TCL语言介绍

Tcl(Tool Command Language,工具命令语言)是一种灵活的脚本语言,与 Python 和 C++ 相比,它具有不同的语法和设计理念。Tcl 的设计侧重于字符串处理、集成和易于嵌入。

基本语法

- 命令和参数

Tcl 的基本单位是命令,每个命令由一个命令名和一系列参数组成,参数之间由空格分隔。

1 | |

- 注释

在 Tcl 中,注释以井号 # 开始,直到行末。

1 | |

- 变量

变量通过 set 命令定义,不需要声明类型。使用 $ 符号来访问变量。

1 2 | |

- 字符串

字符串可以用双引号(处理变量和转义字符)或大括号(原样输出,不进行任何替换)括起来。

1 2 3 | |

控制结构

- if 语句

1 2 3 4 5 6 7 | |

- 循环

for 循环类似于 C++ 和 Python 中的 for 循环。 foreach 循环用于遍历列表。

1 2 3 4 5 6 7 8 | |

列表和字典

- 列表

1 2 | |

- 字典

1 2 | |

函数(过程)

在 Tcl 中,函数被称为“过程”(procedure),使用 proc 关键字定义。

1 2 3 4 | |

文件读写

1 2 3 4 | |

参考

- Intel® Quartus® Prime Pro Edition Help version 21.3 - file types Definition

- 英特尔® Quartus® Prime 设计软件支持中心资源 |英特尔 (intel.cn)

- https://community.intel.com/t5/Intel-Quartus-Prime-Software/Quartus-version-control-methodology/m-p/1479729

- Intel® Quartus® Prime Pro Edition Help version 23.1 - ::quartus::project

- GitHub - intel/fpga-partial-reconfig: Tutorials, scripts and reference designs for the Intel FPGA partial reconfiguration (PR) design flow