接前面FGPA小记,试着学习一下FGPA基础知识。Intel提供了免费的Quartus Prime Lite版本,不妨从它开始。Quartus Prime 是 Quartus II的后续产品,首次发布于2015年,紧随Intel收购Altera之后。

从哪儿开始

本文内容使用 Quartus Prime Lite 23.1 进行测试,从Quaruts的GUI操作开始,看看其后台是如何工作的

不妨,先从一个最简单的Verilog程序开始

一步一步操作看看

- 创建工程:.qpf/.qsf

- 添加源码文件:.v

- 编译:生成 .sof

- 引脚分配:修改.qsf

- 再次编译

- 编程和配置

通过向导创建一个空工程

会生成2个文件

- mytest1.qpf

- mytest1.qsf

这两个都是文本文件。

前者工程文件,只有三行:

1 2 3 4 5 | |

后者是设置文件。包含使用的FPGA芯片,顶层入口名TOP_LEVEL_ENTITY,以及要支持的第三方EDA软件等:

1 2 3 4 5 6 7 8 9 10 11 | |

添加设计输入文件

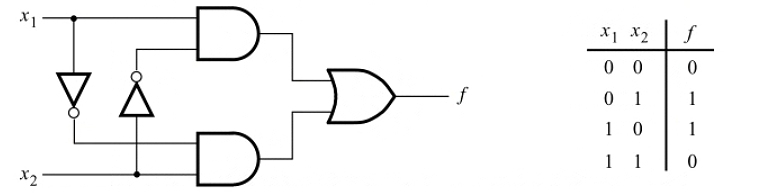

添加一个verilog文件,mytest1.v,内容如下:

1 2 3 | |

注意,网上很多资料中,模块定义都是采用如下(标准化之前的 Verilog-95 风格)的写法,信号类型wire可以省略:

1 2 3 4 5 | |

注意:这个模块名要和qsf配置文件中

TOP_LEVEL_ENTITY设置的一样!(类似于C中的入口函数)

加入工程之后,qsf文件中多了如下一行:

1 | |

执行编译

直接点击菜单中的开始编译。后台会执行如下命令:

1 2 3 4 | |

命令介绍:

- map:映射(mapping),将源代码(Verilog或VHDL)转换成某种内部表示。

- fit:适配(fitting),根据目标FPGA设备的资源和约束来优化和防止设置逻辑

- asm:汇编,将适配阶段生成的数据转换成可用于FPGA的二进制文件

- sta:静态时序仿真(static timng analysis),检查时钟速度、延迟等是否满足设计要求。

选项介绍:

--read_settings_files=on读取qsf配置文件,比如用到里面的TOP_LEVEL_ENTITY--write_settings_files=off不写入qsf配置文件,避免配置文件被修改xxxxx:项目名称或顶层文件名-c xxxxx:指定配置文件名

编译结果:

- 产生

db、incremental_db、output_files三个目录 - 在

output_files中生成:mytst1.sof 文件!!

引脚分配(Pin Assignment)

在上面的编译过程中,我们没有分配引脚,Quartus会自动选择了引脚。引脚指定通过菜单Assignments->Assignment Editor或Assignments->Pin Planner。

指定结果存在qsf配置文件中

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 | |

注意看其中set_location_assignment那几行。

为了指定引脚,我们DEVICE也不能选择AUTO,注意对比

set_global_assignment -name DEVI那一行。

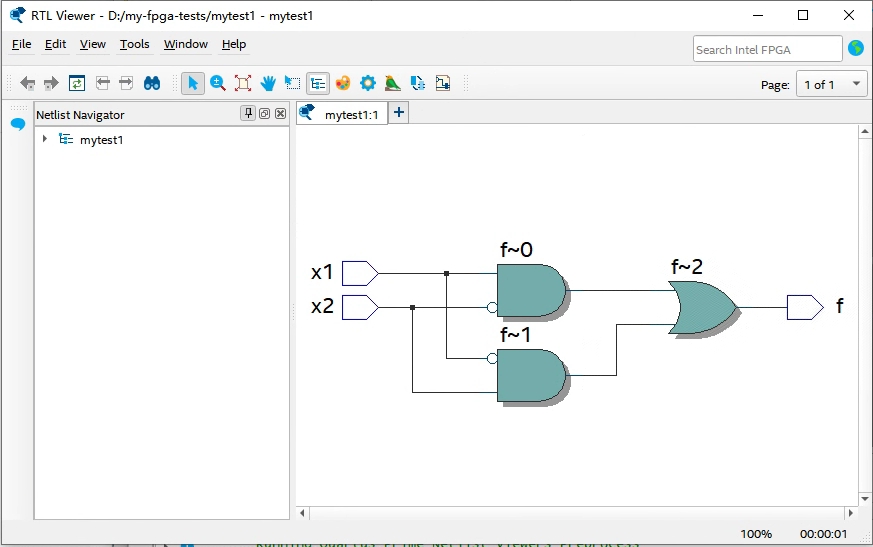

综合后结果查看

通过Tools->NetList Viewers->RTL Viewer,可以查看综合后结果:

编程和配置(Programming and Configuring)

编译后的结果可以通过USB-Blaster烧写器配置到FPGA中。使用Quartus中的Programming工具。

为工程生成Tcl文件

通过 Project->Generate Tcl file for Project... 可以生成如下一个tcl文件:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 | |

除了可以再Quartus Prime 界面中执行这个脚本。还可以直接在命令行下面执行

1 | |

其实,我们只需要保留这个.tcl文件和.v文件就够了。项目文件可以由这个脚本自动生成。

归档文件 .qar

.qar 文件是为了在 Quartus Prime 内部使用而设计的,不同于通用压缩格式 如 zip 或 rar,因此需要通过 Quartus Prime 软件来创建和解压。

它弹出的对话框,对我们理解文件类别会有帮助

创建 .qar 文件:

在 Quartus Prime 中,可以通过项目菜单选择“Archive Project”(归档项目)来创建 .qar 文件。这将打开一个对话框,允许用户选择要包括在归档中的特定文件和设置。

还原 .qar 文件:

要还原 .qar 文件,只需在 Quartus Prime 中选择“File”(文件)菜单下的“Open Project”(打开项目),然后选择 .qar 文件。Quartus 将解压缩归档并还原项目的所有内容。

配置文件(烧写文件)

前面编译的结果是 .sof文件,这个文件通常调试,正式发布的话,一般需要转成.pof文件或.jic文件

- .sof 文件(SRAM Object File):这是一个二进制文件,包含 FPGA 的配置数据,通常在开发阶段用于直接通过 JTAG 或其他接口将配置下载到 FPGA 的 SRAM。

- .pof 文件(Programmer Object File):这是一个用于永久编程 FPGA 或 CPLD 的二进制文件,适用于需要将配置数据永久存储在设备中的情况。

- .jic文件(JTAG Indirect Configuration File):这个文件用于定义通过 JTAG 间接配置 FPGA 时所需的数据和参数。

通过 Quartus Prime菜单File->Convert Programming Files... 可以调出这个转换页面。

一些表格

文件后缀

通过File -> Open菜单,可以看到它支持如下众多的文件类型:

| 类别名称 | 文件后缀 | 备注 |

|---|---|---|

| Design Files | .tdf .vhd .vhdl .v .vlg .verilog .sv .vqm .edf .edif .edn .cpp .mdl .h .gdf .bdf .qip .qdb .cmp .qxp .smf .qsys .ip | |

| Project Files | *.qpf | |

| Quartus Prime Archive Files | *.gar | |

| Quartus Prime Design Template Files | *.par | |

| Other Source Files | .inc .v .vlg .vh .verilog .pkg .bsf .sym .stp .lai .mif .hex .lmf .dpf *.ipx | |

| Graphic Files | .gdf .bdf .bsf .sym | |

| Signal Tap Logic Analyzer Files | *.stp | |

| IP Variation Files | .gip .qsys .sip .ip | |

| Logic Analyzer Interface Files | *.lai | |

| In-System Sources and Probes Files | *.spf | |

| State Machine Editor Files | *.smf | |

| Test Bench Output Files | .wht .vt | |

| Memory Files | .mif .hex | |

| Programming Files | .cdf .sof .pof .jam .jbc .jic .jcf .fcf | |

| Script Files | .tcl .sdc .pdc .gip *.sip | |

| HTML/Text-format Report Files | .rpt .csfrpt .sim.rpt .pao .summary .htm .html .csfhtm .csfhtml .sim.htm *.sim.html | |

| Output Files | .qmsg .vo .who .tdo .sdo .tao *.pin |

手册中的表格对后缀解释更详细:

| 文件类型 | 扩展名 | 备注 |

|---|---|---|

| AHDL Include File | .inc | |

| ATOM Netlist File | .atm | |

| Block Design File | .bdf | |

| Block Symbol File | .bsf | |

| BSDL file | .bsd | |

| Chain Description File | .cdf | |

| Comma-Separated Value File | .csv | |

| Component Declaration File | .cmp | |

| Component Description File | _hw.tcl | |

| Compressed Vector Waveform File | .cvwf | |

| Conversion Setup File | .cof | |

| Cross-Reference File | .xrf | |

| database files | .cdb, .hdb, .rdb, .tdb | |

| Design Protocol File | .dpf | |

| Graphic Design File | .gdf | |

| Hexadecimal (Intel-Format) File | .hex | |

| Hexadecimal (Intel-Format) Output File | .hexout | |

| HSPICE Simulation Deck File | .sp | |

| HTML-Format Report File | .htm | |

| I/O Pin State File | .ips | |

| IBIS Output File | .ibs | |

| In System Configuration File | .isc | |

| IP Index File | .ipx | |

| Jam Byte Code File | .jbc | |

| Jam File | .jam | |

| JTAG Debugging Information File | .jdi | |

| JTAG Indirect Configuration File | .jic | |

| Library Mapping File | .lmf | |

| License File | license.dat | |

| Logic Analyzer Interface File | .lai | |

| Memory Initialization File | .mif | |

| Memory Map File | .map | |

| PartMiner edaXML-Format File | .xml | |

| Pin-Out File | .pin | |

| Pin Planner File | .ppf | |

| Programmer Object File | .pof | |

| Programming files | .cdf, .cof | |

| QMSG File | .qmsg | |

| Intel® Quartus® Prime IP File | .qip | |

| Intel® Quartus® Prime Archive File | .qar | |

| Intel® Quartus® Prime Archive Log File | .qarlog | |

| Quartus User-Defined Device File | .qud | |

| Intel® Quartus® Prime Default Settings File | .qdf | |

| Intel® Quartus® Prime Exported Partition File | .qxp | |

| Intel® Quartus® Prime Message Flag Rule File | .frf | |

| Intel® Quartus® Prime Message Suppression Rule File | .srf | |

| Intel® Quartus® Prime Project File | .qpf | |

| Intel® Quartus® Prime Settings File | .qsf | |

| Intel® Quartus® Prime Workspace File | .qws | |

| Raw Binary File | .rbf | |

| Raw Programming Data File | .rpd | |

| Routing Constraints File | .rcf | |

| Signal Activity File | .saf | |

| Signal Tap File | .stp | |

| Sources and Probes File | .spf | |

| SRAM Object File | .sof | |

| State Machine File | .smf | |

| Symbol File | .sym | |

| Synopsys® Design Constraints File | .sdc | |

| Tab-Separated Value File | .txt | |

| Tabular Text File | .ttf | |

| Tcl Script File | .tcl | |

| Text Design File | .tdf | |

| Text-Format Report File | .rpt | |

| Token File | ted.tok | |

| Vector Table Output File | .tbl | |

| Vector source files | .tbl, .vwf, .vec | |

| Vector Waveform File | .vwf | |

| Verilog Design File | .v, .vh, .verilog, .vlg | |

| Verilog Output File | .vo | |

| Verilog Quartus Mapping File | .vqm | |

| Verilog Test Bench File | .vt | |

| Value Change Dump File | .vcd | |

| Version-compatible database files | .atm, .hdbx, .rcf, .xml | |

| VHDL Design File | .vhd, .vhdl | |

| VHDL Output File | .vho | |

| VHDL Test Bench File | .vht | |

| XML files | .cof, .stp, .xml | |

| Waveform files | .scf, .stp, .tbl, .vec, .vwf | |

| Waveform Settings File | .wsf |

补遗:名字变化

在Intel收购Altera之后,一些工具和组件的名称发生了变化:

| Altera 名称 | Intel® 名称 | 备注 |

|---|---|---|

| Qsys | Platform Designer | 用于设计和配置FPGA内的IP组件和连接的系统集成工具。 |

| TimeQuest | Timing Analyzer | 进行时序验证和分析,确保设计满足时序要求的工具。 |

| EyeQ | Eye Viewer | 用于分析高速串行通道眼图的模拟工具。 |

| JNEye | Advanced Link Analyzer | 高级链路分析工具,适用于复杂的高速数据传输系统设计分析。 |

参考

- Intel® Quartus® Prime Pro Edition Help version 21.3 - file types Definition

- 英特尔® Quartus® Prime 设计软件支持中心资源 |英特尔 (intel.cn)

- https://community.intel.com/t5/Intel-Quartus-Prime-Software/Quartus-version-control-methodology/m-p/1479729

- Intel® Quartus® Prime Pro Edition Help version 23.1 - ::quartus::project

- GitHub - intel/fpga-partial-reconfig: Tutorials, scripts and reference designs for the Intel FPGA partial reconfiguration (PR) design flow