接前面EDA软件小记,继续学习。

FPGA(Field Programmable Gate Array 现场可编程门阵列)是一种高度灵活的数字集成电路,广泛应用于多种行业和技术领域。

知名厂家

一些知名的FPGA厂家:

- AMD Xilinx:/ˈzaɪ.lɪŋks/

- Intel (前Altera):/ˈæl.tɛr.ə/

- Microchip Technology(前 Microsemi, 前Actel):

- Lattice Semiconductor:

- Achronix:

列个表格:

| FPGA 厂家 | FPGA 系列 | 开发环境 |

|---|---|---|

| AMD Xilinx /ˈzaɪ.lɪŋks/ | Virtex, Kintex, Artix, Zynq | Vivado /vɪˈvɑː.doʊ/ Design Suite, Vitis /ˈvaɪ.tɪs/ |

| Intel (前 Altera /ˈæl.tɛr.ə/) | Stratix, Arria, Cyclone | Intel Quartus Prime |

| Microchip (前 Microsemi, 前 Actel) | PolarFire, SmartFusion2, IGLOO2, RTG4 | Libero SoC Design Suite |

| Lattice Semiconductor | Mach, LatticeECP3, iCE40 | Lattice Diamond, Radiant Software |

| Achronix | Speedster7t | Achronix CAD Environment (ACE) |

Intel

对于Intel,FPGA的几个系列:

| 系列名称 | 发布时间 | 描述 | 特点 | 常见应用领域 |

|---|---|---|---|---|

| Agilex | 2019 | 最新一代的高性能FPGA系列 | 超高性能、能效优化 | 数据中心加速、高速网络、AI加速 |

| Stratix /ˈstræ.tɪks/ | Stratix: 2002 Stratix II: 2004 Stratix III: 2007 Stratix IV: 2008 Stratix V: 2010 Stratix 10: 2016 |

高端FPGA系列,提供最高性能 | 高性能、高集成度 | 数据中心、高性能计算、网络基础设备、军事系统 |

| Arria /ˈɑː.ri.ə/ | Arria GX: 2008 Arria II: 2009 Arria V: 2011 Arria 10: 2013 Arria V GZ: 2013 |

中高端FPGA系列,性能与成本平衡 | 性能优良、成本效益较高 | 无线通信、广播、数据处理 |

| Cyclone | Cyclone: 2002 Cyclone II: 2004 Cyclone III: 2007 Cyclone IV: 2009 Cyclone V: 2012 Cyclone 10: 2017 |

成本和功耗敏感的低端FPGA系列 | 成本效益高、低功耗 | 消费电子、工业控制、汽车电子 |

| MAX | MAX 7000: 1996 MAX 3000A: 1997 MAX II: 2004 MAX V: 2010 MAX 10: 2013 |

CPLD系列,适用于简单的逻辑集成 | 小型化、低功耗 | 简单逻辑控制、I/O扩展、设备管理 |

| SoC FPGA | Cyclone V SoC: 2012 Arria V SoC: 2013 Arria 10 SoC: 2016 |

结合ARM处理器和FPGA的产品 | 处理器功能强大、可编程灵活 | 嵌入式系统、需要硬件加速的应用 |

Quartus Prime Lite是 Intel 提供的免费 FPGA 设计软件版本,主要支持低成本 FPGA 设备。它包括设计和编程的基本功能,但在某些高级功能和设备支持方面有所限制。它支持的系列:

- Arria II

- Cyclone IV

- Cyclone V

- Cyclone 10 LP

- MAX II, MAX V

- MAX 10

FPGA 组成

FPGA的主要组成部分:可配置逻辑块,输入输出块、互联网络

| 组件分类 | 英文名称 | 功能描述 | 特点或组成元素 |

|---|---|---|---|

| 可配置逻辑块/逻辑阵列块 | CLBs (Configurable Logic Blocks) / LABs (Logic Array Blocks) | 核心组成部分,执行各种逻辑功能 | 包括查找表(LUTs)、寄存器、逻辑门等 |

| 输入/输出块 | IOBs (Input/Output Blocks) | 链接FPGA与外界,负责数据输入和输出 | 支持不同电压和信号标准 |

| 互连网络 | Interconnection Network | 连接FPGA内部的各个逻辑和功能块,传输数据 | 路由通道、交叉开关、可编程连接点 |

| 时钟管理模块 | Clock Management Modules | 提供和管理时钟信号,同步操作 | 包括PLLs和时钟分配网络 |

| 特定功能块 | Specialized Function Blocks | 优化特定应用的性能和资源使用 | 如DSP块、高速串行接口、内置RAM块 |

| 配置与控制逻辑 | Configuration and Control Logic | 管理配置过程,包括加载配置数据至逻辑和功能块 | 确保FPGA按设计运行 |

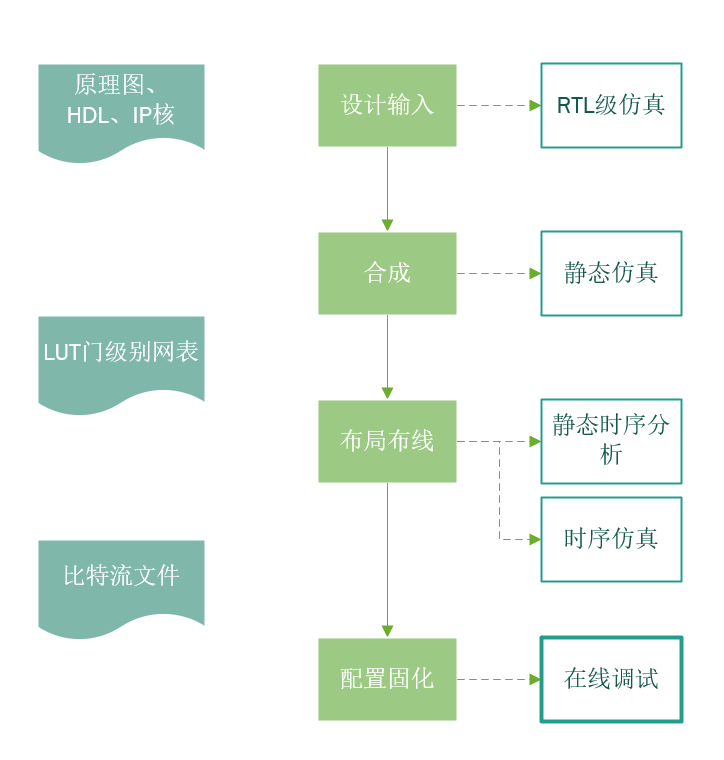

FPGA 开发流程

| 开发阶段 | Intel 使用的工具 | Xilinx 使用的工具 |

|---|---|---|

| 设计输入 | Intel Quartus Prime | Vivado Design Suite |

| 功能仿真 | ModelSim-Intel Edition | Vivado Simulator |

| 合成(Synthesis) | Intel Quartus Prime | Vivado Design Suite |

| 布局布线( Placement/Routing) | Intel Quartus Prime | Vivado Design Suite |

| 时序分析 | Intel Quartus Prime | Vivado Timing Analyzer |

| 生成比特流 | Intel Quartus Prime | Vivado Design Suite |

| 硬件加载(配置) | Intel Quartus Programmer | Vivado Hardware Manager |

| 调试与优化 | SignalTap II Logic Analyzer | Vivado Logic Analyzer |

| 文档与发布 | - | - |

设计输入

- 硬件描述语言(HDL)编程:

- 常用的 VHDL和Verilog

- 以及更先进的SystemVerilog

- 高级综合工具:

- 高级综合工具HLS(High-Level Synthesis):比如 AMD Xilinx Vivado HLS,Intel HLS Compiler 允许C/C++,而后转成HDL代码。

- 模型驱动开发:比如Matlab或Simulink,通过模型或仿真来生成可在FPGA上运行的代码

- 图形化设计

- FPGA设计软件:通过拖动不同的模块来创建设计

- 封装好的IP核

- 嵌入式软件开发

- 软核处理器:比如AMD Xilinx的MicroBlaze和Intel的Nios II,是FPGA内实现的软核,可以运行C/C++代码,实现软件与硬件集成

- 操作系统支持:在FPGA上运行精良及系统比如FreeRTOS

合成(Synthesis)

合成 又分为几个阶段:

- 编译 (Compilation) - 这一步骤涉及将设计者使用硬件描述语言(如VHDL或Verilog)编写的代码,转换为更低级的表示形式(例如,门级网表)。这是合成过程的一部分,目的是解析和优化源代码,准备进行下一步的逻辑映射。

- 逻辑合成 (Logic Synthesis) - 在这个阶段,编译后的代码被进一步转换为逻辑门和电路的集合。这包括优化逻辑以减少所需资源的使用和提高性能。

- 映射 (Mapping) - 映射步骤涉及将合成后的门级网表映射到FPGA的具体逻辑资源上,如查找表(LUTs)、触发器(Flip-Flops)和其他可配置逻辑块(CLBs)。这个过程需要 考虑FPGA的物理架构,确保设计有效利用FPGA的资源,并满足时序和功能要求。

开发环境

首先,各家有自己的IDE环境

- AMD Xilinx Vivado: 针对 Xilinx FPGA 设计的开发环境,包括合成、放置和布线、仿真等工具。

- Intel Quartus Prime: 用于 Intel FPGA 设计的开发平台,同样提供全套设计、仿真和优化工具。

- Microsemi Libero: 针对 Microsemi FPGA 设计的软件工具。

- Lattice Diamond: 用于 Lattice FPGA 设计的软件环境。

仿真环境

ModelSim 是一款广泛使用的硬件仿真工具,由 Mentor Graphics(现为 Siemens EDA 的一部分)开发。它支持 VHDL、Verilog 和 SystemVerilog 等硬件描述语言,用于在 FPGA 和 ASIC 设计流程中模拟和验证数字系统的行为。

合成

一些高级综合工具,它专门为 FPGA 设计提供支持,但它本身并不限定于特定品牌的 FPGA:

- Synopsys Synplify:高性能合成工具,适用于 FPGA 和 ASIC。支持 Verilog和VHDL语言。

- Candence Genus Snthesis Solution,提供高级综合和优化功能,适用于复杂的ASIC和FPGA设计。支持Verilog、VHDL和SystemVerilog语言。

合成完成后,仍然需要使用 厂家的EDA来完成后续的布局和布线(Place and Route)以及生成可用于 FPGA 编程的最终文件。确保了设计在特定硬件上的最优性能和资源利用。

开源工具

有些命令行工具:

| 工具名称 | 支持语言 | 主要用途 | 优点 | 缺点 |

|---|---|---|---|---|

| Icarus Verilog | Verilog | 仿真 | - 免费开源 - 跨平台支持 - 社区支持良好 |

- 只支持 Verilog - 功能相对基础 |

| GHDL | VHDL | 编译和仿真 | - 完全开源,使用 GCC 技术 - 提供良好的 VHDL 语言覆盖和符合性 - 支持多种操作系统 |

- 没有集成的图形用户界面(GUI) - 只支持 VHDL |

| Verilator | Verilog | 将 Verilog 转换为 C++/SystemC | - 生成的仿真速度非常快 - 支持大规模复杂的设计 - 可与其他测试框架集成 |

- 只支持 Verilog 的子集 - 缺少图形化界面和高级调试工具 |

| Yosys | Verilog | 逻辑综合 | - 强大的综合工具,支持 RTL Verilog - 适用于 FPGA 和 ASIC 设计 - 可以与其他工具链集成 |

- 主要支持 Verilog - 可能缺乏一些先进的优化和分析功能 |

配置(烧写)

不会编程,先了解下烧写还是可以的...

各个厂家配置文件(待烧写文件)后缀均有不同

| 制造商 | 比特流文件后缀 | 烧写器工具 |

|---|---|---|

| AMD Xilinx | .bit, .bin | Vivado Hardware Manager, Xilinx Platform Cable USB |

| Intel | .sof, .pof, .jic | Quartus Prime Programmer, USB-Blaster, USB-Blaster II |

| Microsemi | .stp | FlashPro, Libero SoC |

| Lattice | .bin, .jed | Lattice Diamond Programmer, ispVM System |

具体看一下Intel的比特流文件后缀:

- .sof (SRAM Object File) - 用于将配置直接加载到FPGA的SRAM中。

- .pof (Programmable Object File) - 用于永久存储配置到FPGA连接的外部设备(例如,EPROM或闪存)。

- .jic (JTAG Indirect Configuration File) - 用于通过JTAG接口对外部配置设备进行编程。

- .hex- 虽然用于记录二进制数据,Intel HEX 文件本身是文本格式,使用ASCII字符表示,便于阅读和编辑。每一行Intel HEX文件都称为一条“记录”。这条记录包括长度、地址、记录类型、数据和校验和等字段。

hex文件示例:

1 2 3 | |

烧写方式(配置模式)

FPGA有多种方式进行配置:

- JTAG接口。需要JTAG线缆(烧写器)连接FPGA和计算机主机

- USB编程器。许多FPGA开发版会配备USB接口,允许适用USB连接进行配置。

- SD卡或其他存储介质。一些FPGA支持从SD卡或其他介质自动加载配置文件。

- 通过外部设备(如微控制器)。FPGA 也可以通过外部微控制器进行烧写,该微控制器将配置文件从某种存储介质(如 SPI 闪存)加载到 FPGA。

以Intel FPGA为例,软件Quartus Prime Programmer有4种编程(programming)模式:

- JTAG:同上

- In-Socket:将设备物理放置到有多个电气接触点的座中,这些触点和设备引脚对应,直接对设备配置存储器进行编程。用于批量编程或者设备安装到最终产品之前进行编程。使用专用设备(APU:Altera Programming Unit)

- Passive Serial:串行编程模式。通过几个信号线(DATA、CLOCK、nCONFIG、nSTATUS)顺序发送。速度慢,但硬件简单,成本低。发送方可以是Quartus Prime Programmer或者其他MCU设备。

- Active Serial:使用外部闪存来存储配置文件,FPGA上电时,自动加载配置。

烧写工具与步骤

每个FPGA制造商都提供了配套的配置软件,用于烧写和调试FPGA。对于Intel FPGA:

- Quartus Prime Programmer - Quartus软件的一部分,用于配置和编程Intel FPGA。

- USB-Blaster 和 USB-Blaster II - 官方的JTAG下载电缆,支持配置和调试。

烧写主要步骤:

- 连接FPGA开发板到计算机主机

- 打开配置软件,并选择正确的配置文件

- 选择目标设备,并确认所有连接和设置无误。

- 启动烧写过程,并关注过程中的状态,确保无错误

- 烧写完成后,重启FPGA设备以加载新的配置。

关于JTAG

JTAG (Joint Test Action Group) 是一种广泛使用的标准,正式名称为 IEEE 1149.1,最初设计用于测试印刷电路板(PCB)上的连接故障,后来发展为一个功能强大的工具,用于芯片的编程、调试和测试。JTAG 不仅用于 FPGA 编程,也广泛应用于微处理器、微控制器等集成电路的调试。

JTAG 使用一组标准化的信号线来传输数据至目标设备。通常包括:

- TCK(时钟)

- TMS(模式选择)

- TDI(数据输入)

- TDO(数据输出)

- TRST(可选的复位线)

通过这些线,可以直接向 FPGA 内部的配置存储器发送配置数据。

参考

- https://en.wikipedia.org/wiki/Field-programmable_gate_array

- 九个步骤完成FPGA开发全流程,每一步都不能少!